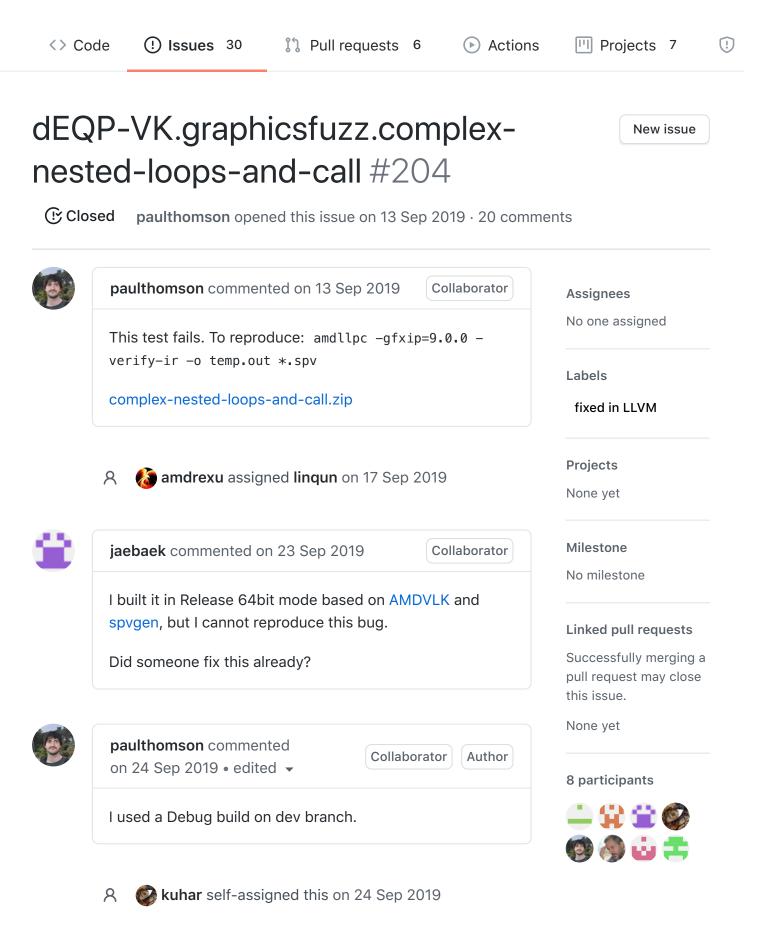

amdrexu unassigned linqun on 25 Sep 2019

ጸ

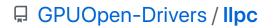

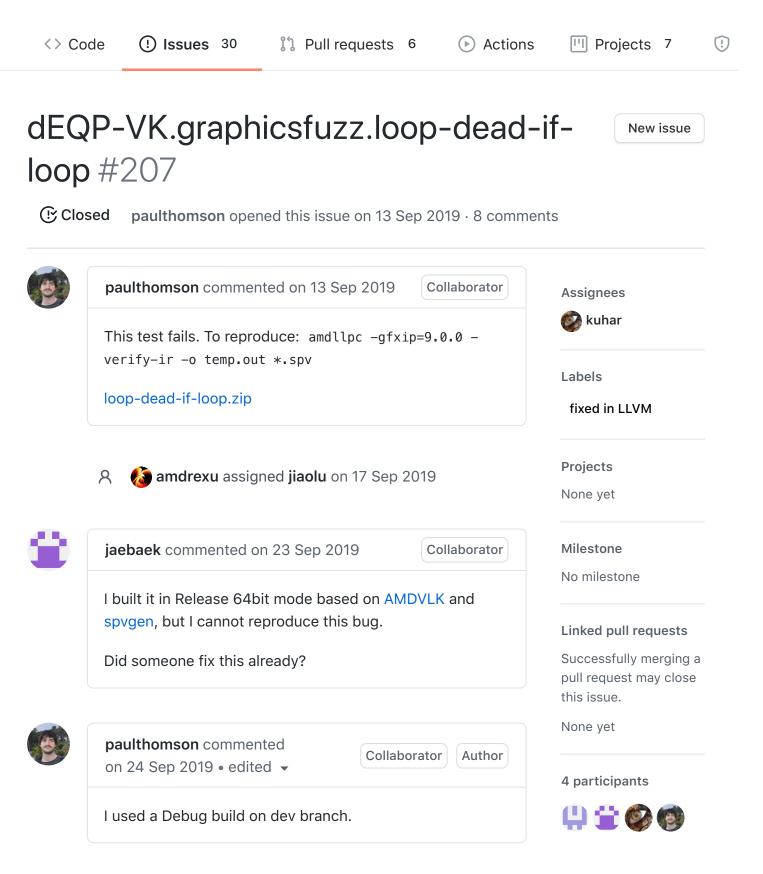

kuhar commented on 25 Sep 2019 • edited •

Collaborator

Seems like there is a bug in SILowerI1Copies.cpp (an LLVM MachineFunction pass).

It happens during the 54th iteration of the inner for loop over machine instructions in

SILowerI1Copies::lowerPhis when a phi has a use in the same machine basic block:

```

bb.39 (%ir-block.176):

; predecessors: %bb.38

successors: %bb.41(0x40000000),

%bb.42(0x40000000); %bb.41(50.00%),

%bb.42(50.00%)

```

```

%457:vgpr_32 = PHI %458:vgpr_32, %bb.38

%153:sreg_64 = PHI %315:vreg_1, %bb.38 ;

<== def

%154:vgpr_32 = PHI %316:vgpr_32, %bb.38

%155:vgpr_32 = PHI %316:vgpr_32, %bb.38

%156:vgpr_32 = PHI %316:vgpr_32, %bb.38

%320:sreg_64_xexec = COPY %153:sreg_64 ;

<== use

%319:vgpr_32 = V_CNDMASK_B32_e64 0, 0, 0, 1,

%320:sreg_64_xexec, implicit $exec

%321:sreg_64 = S_MOV_B64 -1

%318:vreg_1 = COPY %321:sreg_64

```

\$vcc = S\_AND\_B64 \$exec, \$vcc, implicit def

\$scc

S\_CBRANCH\_VCCNZ %bb.41, implicit \$vcc

S\_BRANCH %bb.42

The pass attempts to create a new register and replace the Phi with a new register placed at the end of the block. This is how the machine basic blocks looks at the end of that loop iteration:

```

bb.39 (%ir-block.176):

; predecessors: %bb.38

successors: %bb.41(0x40000000),

%bb.42(0x40000000); %bb.41(50.00%),

%bb.42(50.00%)

```

%457:vgpr\_32 = PHI %458:vgpr\_32, %bb.38

```

%584:sreg_64 = PHI %315:vreg_1, %bb.38

;

<== NewReg (old instruction, will be erased)</pre>

%154:vgpr_32 = PHI %316:vgpr_32, %bb.38

%155:vgpr_32 = PHI %316:vgpr_32, %bb.38

%156:vgpr_32 = PHI %316:vgpr_32, %bb.38

%320:sreg_64_xexec = COPY %153:sreg_64

;

<== use

%319:vgpr_32 = V_CNDMASK_B32_e64 0, 0, 0, 1,

%320:sreg_64_xexec, implicit $exec

%321:sreg_64 = S_MOV_B64 -1

%318:vreg_1 = COPY %321:sreg_64

%322:sreg_32_xm0 = S_MOV_B32 1

%323:sreg_32 = IMPLICIT_DEF

V_CMP_NE_U32_e32 killed %322:sreg_32_xm0,

%319:vgpr_32, implicit-def $vcc, implicit $exec

$vcc = S_AND_B64 $exec, $vcc, implicit-def

$scc

%153:sreg_64 = IMPLICIT_DEF

;

<== DstReg (new instruction, to be used instead)</pre>

S_CBRANCH_VCCNZ %bb.41, implicit $vcc

S BRANCH %bb.42

```

After this iteration, the function verifiers complains that the definition doesn't dominate the use. I think that the new value from the MachineSSAUpdater should be placed before the use, instead of at the end of the block, which would require a small modification to the MachineSSAUpdater.

I hope that this makes sense and I'd really appreciate some tips/relevant documentation if you have any. I'll resume the investigation tomorrow from this point.

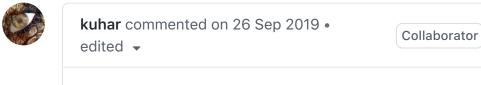

trenouf commented on 26 Sep 2019

Collaborator

Hi Jakub

I'll pass this on to Matt and Stas (AMD engineers on the compute side), who look like the people most linked with SILowerI1Copies, and see what we get back.

nhaehnle commented on 26 Sep 2019 • edited -

Collaborator

I haven't been able to do a full analysis on this and will have to take a closer look at the CFG overall. What I *can* say is that the new value %153 is almost certainly correct where it is (or at least "more correct" than moving it would be). This is because we certainly want a defined value to be used in the V\_CNDMASK\_B32, since thats what's happens in the original code.

That is to say, it seems more likely that the correct fix would be to change the use of %153 into a use of some other newly generated instruction that does dominate.

arsenm commented on 26 Sep 2019 • edited -

This is some confusing shadowing to me; I would assume the second MBB really intended to be the current iterated block, not the predecessor

for (MachineBasicBlock \*MBB : PIA.predecessors())

SSAUpdater.AddAvailableValue(MBB,

insertUndefLaneMask(\*MBB));

kuhar commented on 26 Sep 2019

Collaborator

#### Thanks @trenouf!

**@nhaehnle**, **@arsenm** thank you for looking into this and your insights.

Can you recommend me some resources to learn more about what SILowerI1Copies is trying to achieve and why? I don't fully understand the transformation after reading the header and the implementation files.

To be specific, I'm confused about what values are supposed to flow into the uses in the middle of blocks and what the semantics of implicit defs are.

Without a better understanding of the pass I don't know if I can be of much use when it comes to this bug, unless somebody tells me exactly what is broken here.

arsenm commented on 26 Sep 2019

Fundamentally SILowerI1Copies is a SelectionDAG workaround. In the DAG we don't have the necessary context to know how to treat a boolean value. We use the pseudo register-class VReg\_1, and then SILowerI1Copies sorts out when it's appropriate to use a real lane mask for these values.

trenouf commented on 26 Sep 2019

Collaborator

Stas said:

If it did replace %153 with %584 it should probably also replace its uses with the new %584. I see that COPY left using %153.

A 🚱 kuhar removed their assignment on 26 Sep 2019

#### @trenouf

Stas said:

If it did replace %153 with %584 it should probably also replace its uses with the new %584. I see that COPY left using %153.

Yes, but the new value %584 does not dominate the use, even if the use gets updated.

Nicolai said (in reply to Stas's comment):

%584 may just be an artefact of how the registers are swapped around in order to erase instructions.

nhaehnle commented on 27 Sep 2019

Collaborator

**@kuhar**, I've root-caused a first issue to a subtle bug in the MachineSSAUpdater, but there's a follow-on issue that I'm currently looking at.

kuhar commented on 27 Sep 2019

Collaborator

@nhaehnle OK. Let me know if you need help with this issue.

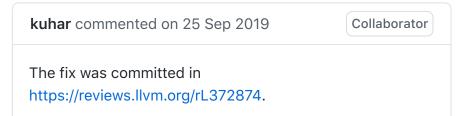

- C nhaehnle added a commit to nhaehnle/llvm-project that referenced this issue on 27 Sep 2019

- MachineSSAUpdater: insert 782f7ff

IMPLICIT\_DEF at top of basic block

...

- C nhaehnle added a commit to nhaehnle/llvm-project that referenced this issue on 27 Sep 2019

- AMDGPU: Propagate undef flag during b2e1caa pre-RA exec mask optimizations ...

**@kuhar**, the branch here with two simple changes allows the problematic shader to compile: https://github.com/nhaehnle/llvm-project/tree/wip-githubllpc-204

I'm currently travelling and not setup to run amber tests. Could you please check whether those changes fully fix the issue in the dEQP-VK test?

kuhar commented on 27 Sep 2019 • edited -

Collaborator

@nhaehnle Applying the patches seems to fix the issue -MIR verifieas correctly now.

nhaehnle commented on 28 Sep 2019

Collaborator

See https://reviews.llvm.org/D68183 and https://reviews.llvm.org/D68184

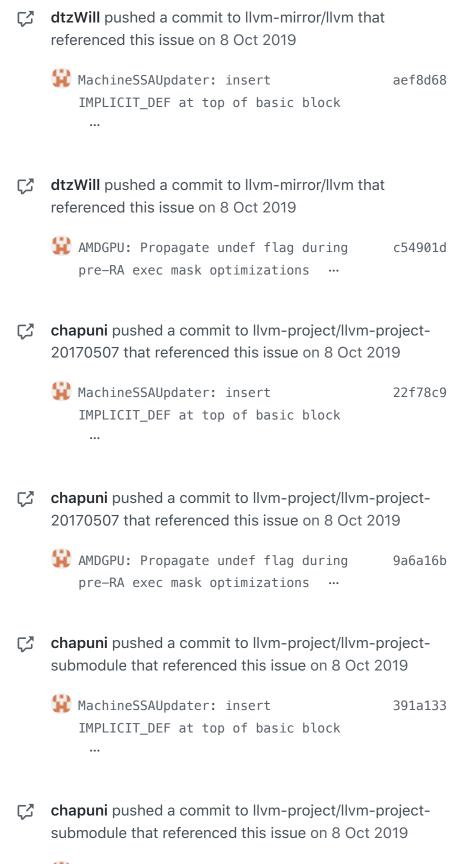

Ilvm-git-migration pushed a commit to llvm/llvm-project that referenced this issue on 8 Oct 2019

MachineSSAUpdater: insert ✓ 7febdb7 IMPLICIT\_DEF at top of basic block •••

Ilvm-git-migration pushed a commit to llvm/llvm-project that referenced this issue on 8 Oct 2019

🙀 AMDGPU: Propagate undef flag during ✓ df6e676 pre-RA exec mask optimizations •••

AMDGPU: Propagate undef flag during 0021f04

pre-RA exec mask optimizations ...

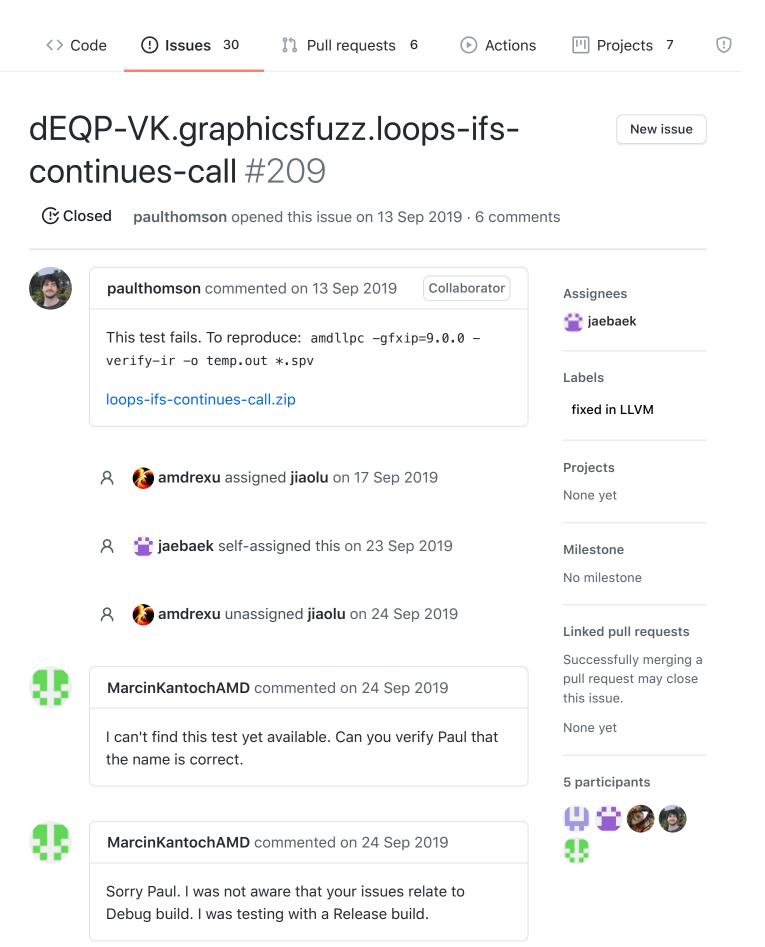

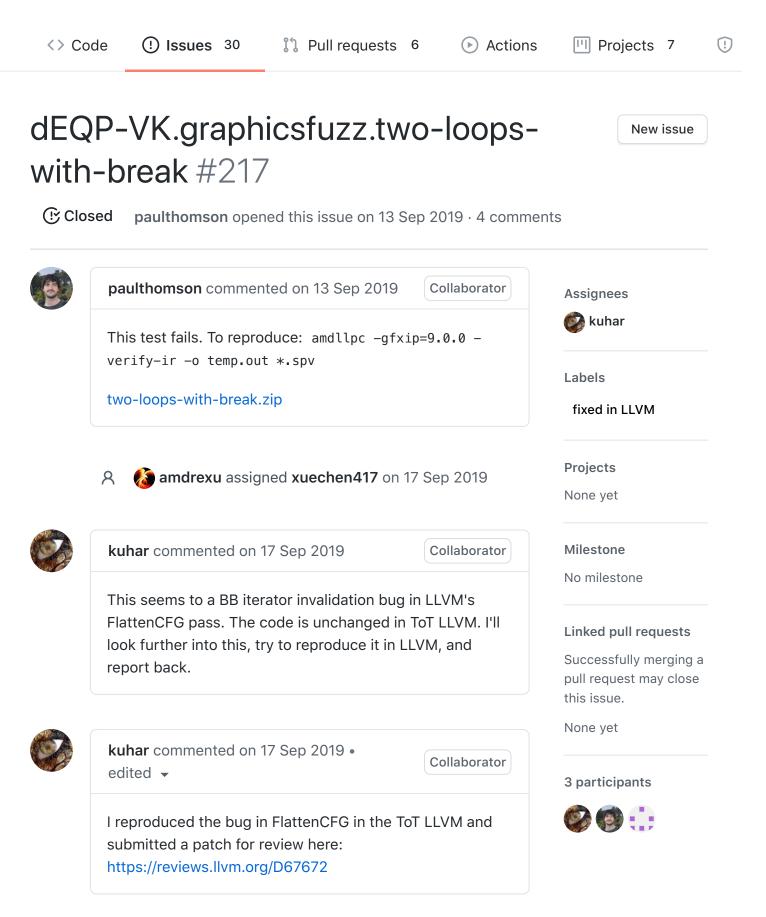

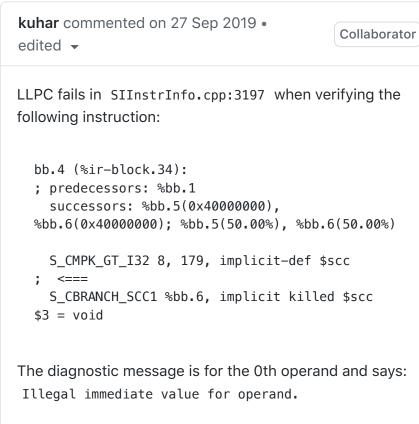

kuhar commented on 24 Sep 2019

Collaborator

I can reproduce in Debug mode on the master branch. Looking into it.

whar self-assigned this on 24 Sep 2019

kuhar commented on 24 Sep 2019 Collaborator

I submitted an LLVM commit fixing the issue here: https://reviews.llvm.org/D67974

8

amdrexu unassigned jiaolu on 25 Sep 2019

kuhar commented on 27 Sep 2019

After doing some cleanup in LLVM when working on this issue, a new issue with MachineDominators surfaced: PHIEIimination lied about preserving MDT. I submitted a fix here: https://reviews.llvm.org/D68154 Not sure if the AMDGPU target uses this part of the machine pass pipeline, but may be work merging in this fix too.

The Machine (Post)Dominators should be fully fixed now by the series of LLVM commits:

- https://reviews.llvm.org/rL372874 : [Dominators] [AMDGPU] Don't use virtual exit node in findNearestCommonDominator.

- https://reviews.llvm.org/rL373341 : [Dominators] [CodeGen] Add MachinePostDominatorTree verification.

- https://reviews.llvm.org/rL373376 : Reapply [Dominators][CodeGen] Clean up MachineDominators.

- https://reviews.llvm.org/rL373377 : [Dominators]

[CodeGen] Fix MachineDominatorTree preservation in PHIElimination.

- https://reviews.llvm.org/rL373378 : [Dominators] [CodeGen] Don't mark MachineDominatorTree as preserved in MachineLICM.

- 5. https://reviews.llvm.org/rL373382 : Add a missing pass in ARM O3 pipeline.

🚫 🚳 kuhar added the fixed in LLVM label on 9 Oct 2019

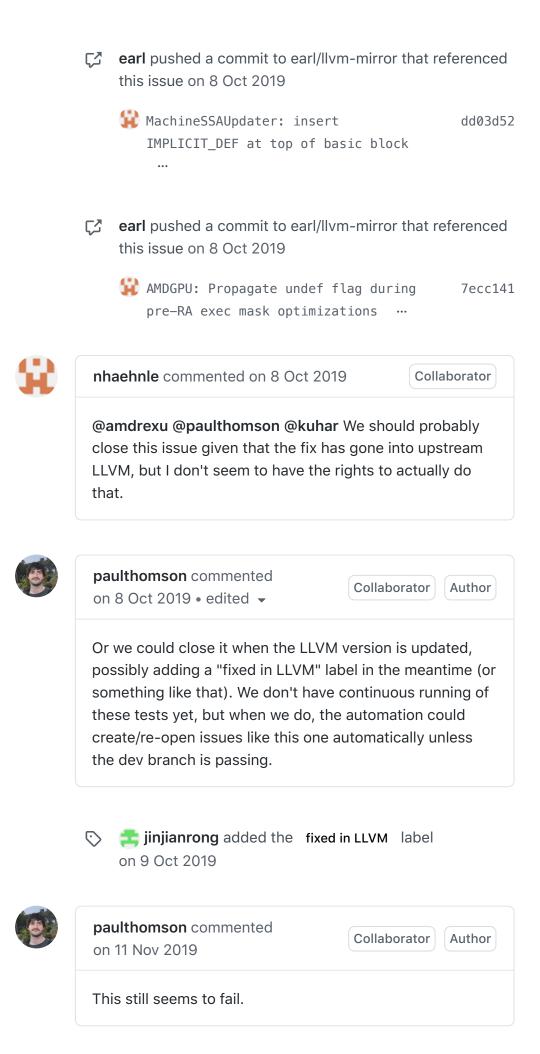

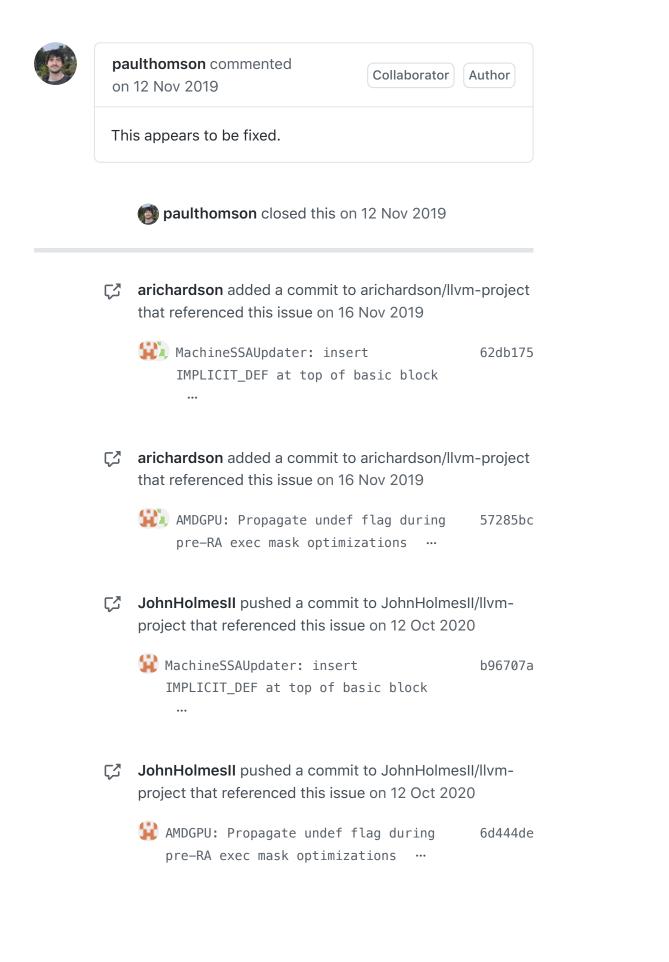

| paulthomson commented<br>on 11 Nov 2019 | Collaborator | Author |

|-----------------------------------------|--------------|--------|

| 01111100 2010                           |              |        |

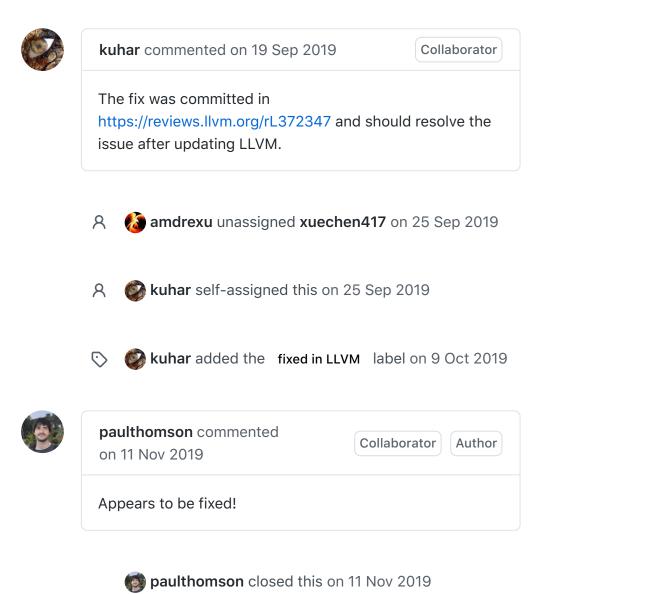

Appears to be fixed!

paulthomson closed this on 11 Nov 2019

|          | paulthomson commented<br>on 24 Sep 2019CollaboratorAuthor                                           |   |

|----------|-----------------------------------------------------------------------------------------------------|---|

|          | Some of the tests are still pending CLs but the AmberScript file and the SPIR-V shader is attached. |   |

|          |                                                                                                     |   |

| ۲        | jaebaek commented on 25 Sep 2019 Collaborator                                                       |   |

|          | Sent a PR: https://reviews.llvm.org/D68032                                                          |   |

|          |                                                                                                     |   |

| ۲        | jaebaek commented on 26 Sep 2019 •<br>edited →                                                      |   |

|          | The PR was merged: <a href="https://www.noise.com">live/live/live/live/live/live/live/live/</a>     |   |

|          | kuhar added the fixed in LLVM label on 9 Oct 2019                                                   | 9 |

| <b>(</b> | paulthomson commented     Collaborator     Author                                                   |   |

|          | Appears to be fixed!                                                                                |   |

|          | paulthomson closed this on 11 Nov 2019                                                              |   |

| <> Co | ode () Issues 30 () Pull requests 6 () Actions                                                                                       | III Projects 7                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

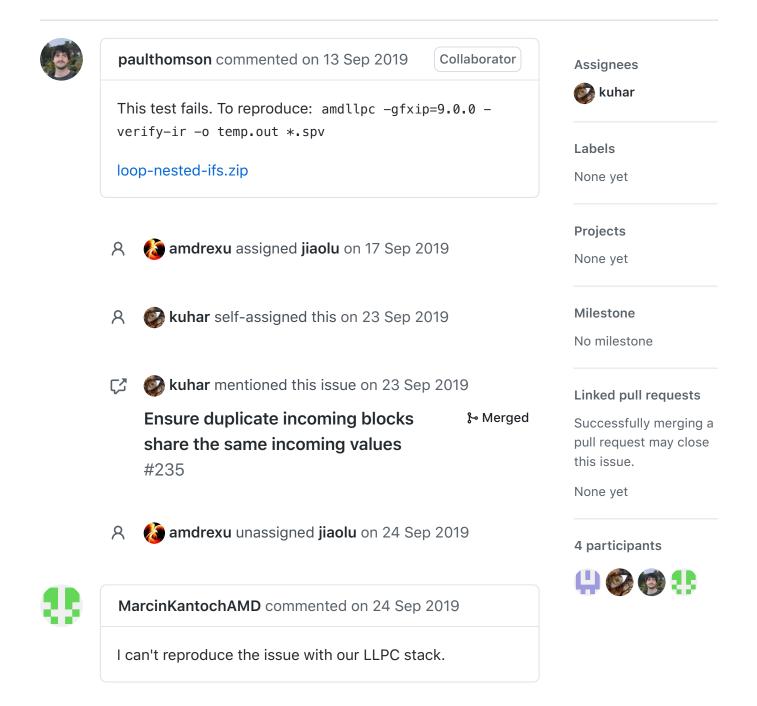

|       | P-VK.graphicsfuzz.call-if-while<br>ch #203<br>sed paulthomson opened this issue on 13 Sep 2019 · 8 comment                           |                                                                                         |

| 0     | paulthomson commented on 13 Sep 2019CollaboratorThis test fails. To reproduce: amdllpc -gfxip=9.0.0 -<br>verify-ir -o temp.out *.spv | Assignees<br>kuhar<br>Labels                                                            |

|       | call-if-while-switch.zip amdrexu commented on 16 Sep 2019 Collaborator                                                               | None yet Projects None yet                                                              |

|       | Are those issues urgent for you? We need to know the priority.                                                                       | <b>Milestone</b><br>No milestone                                                        |

| 0     | paulthomson commented     Collaborator     Author       on 16 Sep 2019     These are not unreast. These are                          | Linked pull requests<br>Successfully merging a<br>pull request may close<br>this issue. |

|       | These are not urgent. Thanks.      amdrexu commented on 17 Sep 2019      Collaborator                                                | None yet 7 participants                                                                 |

|       | Thank you for feedbacks. We will arrange resources to handle those issues.                                                           | 🥸 🧐 🧐 🥶<br>🍪 🛨 🏀                                                                        |

amdrexu commented on 17 Sep 2019

Collaborator

I will assign those issues to developers. If someone else believes he can handle this, feel free to reassign it to yourself and make comments in the issue ticket.

amdrexu assigned linqun on 17 Sep 2019

dnovillo commented on 17 Sep 2019 Collaborator

**@jinjianrong** I will assign them to myself for now. I will reassign as folks start working on them internally.

A 👔 amdrexu unassigned linqun on 25 Sep 2019

A 🕼 kuhar self-assigned this on 26 Sep 2019

Add missing phi entries for duplicate incoming arcs #244

⊱ Merged

kuhar commented on 18 Oct 2019

Collaborator

This issue is fixed and can be closed.

💼 s-perron closed this on 7 Nov 2019

| <> Code | (!) Issues 30 | រះ Pull requests 6 | Actions | Projects 7 | ( |

|---------|---------------|--------------------|---------|------------|---|

|---------|---------------|--------------------|---------|------------|---|

$( \mathbf{I} )$

New issue

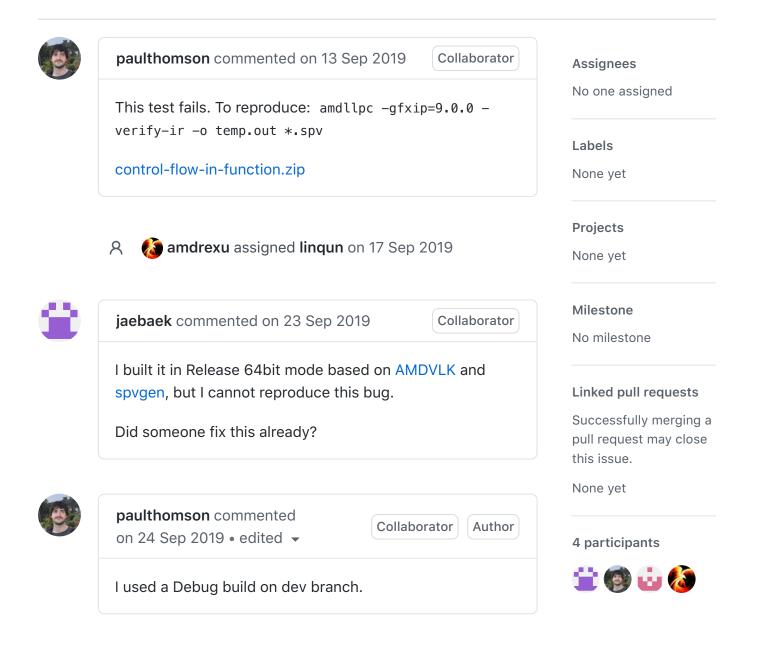

# dEQP-VK.graphicsfuzz.control-flowin-function #205

Closed paulthomson opened this issue on 13 Sep 2019 · 6 comments

paulthomson closed this on 11 Nov 2019

# dEQP-VK.graphicsfuzz.loop-nested-ifs New issue #208

Closed paulthomson opened this issue on 13 Sep 2019 · 8 comments

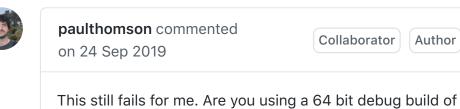

the dev branch?

paulthomson commented Collaborator Author on 24 Sep 2019 amdllpc -gfxip=9.0.0 -verify-ir -o temp.out \*.spv PHI node has multiple entries for the same basic block with different incoming values! %\_llpc\_output\_proxy\_.4.0 = phi float [ %34, %25 ], [ %33, %25 ], [ %40, %35 ], [ 1.000000e+00, %41 ] label %25 %33 = extractelement <4 x float> %spec.select, i32 0 %34 = extractelement <4 x float> %spec.select, i32 0 in function llpc.shader.FS.main ERROR: LLVM FATAL ERROR: Broken function found, compilation aborted!

kuhar commented on 24 Sep 2019CollaboratorI can reproduce it on master in Debug mode.

MarcinKantochAMD commented on 24 Sep 2019

Sorry Paul. I was not aware that your issues relate to Debug build. I was testing with a Release build.

| 6        | paulthomson commented on 24 Sep 2019        | Collaborator Author |

|----------|---------------------------------------------|---------------------|

|          | Yes, sorry I should have made this c        | learer.             |

|          |                                             |                     |

|          | kuhar commented on 9 Oct 2019               | Collaborator        |

|          | This issue is fixed and can be closed       | d.                  |

|          |                                             |                     |

| <b>(</b> | <b>paulthomson</b> commented on 11 Nov 2019 | Collaborator Author |

|          | Appears to be fixed!                        |                     |

|          |                                             |                     |

paulthomson closed this on 11 Nov 2019

| <> Code | (!) Issues 30 | រង Pull requests 6 | Actions | Projects 7 | ! |

|---------|---------------|--------------------|---------|------------|---|

|---------|---------------|--------------------|---------|------------|---|

New issue

# dEQP-VK.graphicsfuzz.max-mixconditional-discard #210

Closed paulthomson opened this issue on 13 Sep 2019 · 4 comments

| 0 | paulthomson commented on 13 Sep 2019 Collaborator                                                       | Assignees<br>No one assigned                |

|---|---------------------------------------------------------------------------------------------------------|---------------------------------------------|

|   | This test fails. To reproduce: amdllpc -gfxip=9.0.0 -<br>verify-ir -o temp.out *.spv                    | Labels                                      |

|   | max-mix-conditional-discard.zip                                                                         | None yet                                    |

|   | • • • • • • • • • • • • • • • • • • •                                                                   | Projects                                    |

|   | A 🕼 amdrexu self-assigned this on 17 Sep 2019                                                           | None yet                                    |

|   | MarcinKantochAMD commented on 24 Sep 2019                                                               | <b>Milestone</b><br>No milestone            |

|   | I tested today and the test is passing on our LLPC stack.                                               |                                             |

|   |                                                                                                         | Linked pull requests Successfully merging a |

|   | MarcinKantochAMD commented on 24 Sep 2019                                                               | pull request may close<br>this issue.       |

|   | Sorry Paul. I was not aware that your issues relate to Debug build. I was testing with a Release build. | None yet                                    |

|   |                                                                                                         | 4 participants                              |

I don't understand MIR enough to tell what the issue here really is.

| paulthomson commented on 11 Nov 2019 | Collaborator Author |

|--------------------------------------|---------------------|

| Appears to be fixed!                 |                     |

paulthomson closed this on 11 Nov 2019

$(\cdot)$

# dEQP-VK.graphicsfuzz.modf-gl-color New issue #212

Closed paulthomson opened this issue on 13 Sep 2019 · 5 comments

MarcinKantochAMD commented on 24 Sep 2019

Sorry Paul. I was not aware that your issues relate to Debug build. I was testing with a Release build.

amdrexu removed their assignment on 25 Sep 2019

paulthomson commented<br/>on 11 Nov 2019CollaboratorAuthorAppears to be fixed!

paulthomson closed this on 11 Nov 2019

| <> Code | Issues 30 | រ៉ា Pull requests 6 | Actions | Projects 7 | ! |

|---------|-----------|---------------------|---------|------------|---|

|---------|-----------|---------------------|---------|------------|---|

# dEQP-VK.graphicsfuzz.modf-tempmodf-color #213

Closed paulthomson opened this issue on 13 Sep 2019 · 5 comments

| ( <b>B</b> ) | paulthomson commented on 13 Sep 2019 Collaborator                                                                | <b>Assignees</b><br>No one assigned                                                                 |

|--------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

|              | This test fails. To reproduce: amdllpc -gfxip=9.0.0 -<br>verify-ir -o temp.out *.spv<br>modf-temp-modf-color.zip | Labels<br>None yet                                                                                  |

|              | A 🚳 amdrexu self-assigned this on 17 Sep 2019                                                                    | <b>Projects</b><br>None yet                                                                         |

|              | A whar self-assigned this on 18 Sep 2019                                                                         | <b>Milestone</b><br>No milestone                                                                    |

|              | A 🚯 amdrexu removed their assignment on 20 Sep 2019                                                              | Linked pull requests<br>Successfully merging a<br>pull request may close<br>this issue.<br>None yet |

#### 5 participants

New issue

Not whether this input spv is valid. The crash happens when translating the last OpExtInst: OpCapability Shader %1 = OpExtInstImport "GLSL.std.450" OpMemoryModel Logical GLSL450 OpEntryPoint Fragment %main "main" %\_GLF\_color OpExecutionMode %main OriginUpperLeft **OpSource ESSL 310** OpName %main "main" OpName %temp "temp" OpName %\_GLF\_color "\_GLF\_color" OpDecorate %\_GLF\_color Location 0 %void = OpTypeVoid %6 = OpTypeFunction %void %float = OpTypeFloat 32 %v4float = OpTypeVector %float 4 %float\_1 = OpConstant %float 1 %10 = OpConstantComposite %v4float %float\_1 %float\_1 %float\_1 %\_ptr\_Function\_v4float = OpTypePointer Function %v4float %float\_0 = OpConstant %float 0 %13 = OpConstantComposite %v4float %float\_1 %float\_0 %float\_0 %float\_1 %17 = OpExtInst %v4float %1 Modf %13 %\_GLF\_color <==== 0pReturn **OpFunctionEnd**

The second argument to Modf is in address space 65, instead of 5. Due to type mismatch

This seems similar to the issue reported here: KhronosGroup/SPIRV-Cross#1123.

If the input spv is valid, would it be enough to just introduce an address space cast before passing the %\_GLF\_color to Modf ?

Author

I wonder if this is fixed by my outstanding PR #169, which reimplements Modf with a separate ModfStruct and store in the spir-v reader.

I guess the problem at the moment might be that the modf is a library function, so it eventually expands to have a store, but not in time for LowerGlobal to spot that it is a store to an output.

MarcinKantochAMD commented on 24 Sep 2019

I ran the test today and it is passing on our LLPC stack.

MarcinKantochAMD commented on 24 Sep 2019

Sorry Paul. I was not aware that your issues relate to Debug build. I was testing with a Release build.

paulthomson commentedCollaboratoron 11 Nov 2019Collaborator

Appears to be fixed!

kuhar commented on 17 Sep 2019 • edited -

Collaborator

This fails in llpcCompiler.cpp:220: class LlpcDiagnosticHandler : public llvm::DiagnosticHandler { bool handleDiagnostics(const DiagnosticInfo& diagInfo) override { if (EnableOuts() || EnableErrs()) { if ((diagInfo.getSeverity() == DS\_Error) || (diagInfo.getSeverity() == DS\_Warning)) { DiagnosticPrinterRawOStream printStream(outs()); printStream << "ERROR: LLVM</pre> DIAGNOSIS INFO: "; diagInfo.print(printStream); printStream << "\n";</pre> outs().flush(); } . . . } LLPC\_ASSERT(diagInfo.getSeverity() != ==> DS\_Error); return true; } };

With the error message: unsupported dynamic alloca. Not sure what the intention was here -- perhaps to emit diagnostics and terminate on DS\_Error s? In that case, I'd expect to see something like llvm::report\_fatal\_error used instead of the assertion.

Similar applies to issue #214.

lingun commented on 18 Sep 2019

Collaborator

please check whether there are some alloca in the middle of function. if yes, please try to find which pass add it and try to move it to the begin of function.

🔀 🙆 kuhar mentioned this issue on 23 Sep 2019

Do not clone allocas in PeepholeOpt№ Merged#234

A **amdrexu** unassigned **xuechen417** on 24 Sep 2019

MarcinKantochAMD commented on 24 Sep 2019

Hi Paul. I tested today and can't reproduce the issue anymore.

MarcinKantochAMD commented on 24 Sep 2019

Sorry Paul. I was not aware that your issues relate to Debug build. I was testing with a Release build.

| kuhar | commented on 9 Oct 2019 | Colla |

|-------|-------------------------|-------|

|       |                         |       |

Collaborator

This issue is fixed and can be closed.

| paulthomson commented on 11 Nov 2019 | Collaborator Author |

|--------------------------------------|---------------------|

| Appears to be fixed!                 |                     |

paulthomson closed this on 11 Nov 2019

Hi Paul. I tested today and can't reproduce the issue.

MarcinKantochAMD commented on 24 Sep 2019

Sorry Paul. I was not aware that your issues relate to Debug build. I was testing with a Release build.

A **amdrexu** unassigned **xuechen417** on 25 Sep 2019

**s-perron** self-assigned this on 25 Sep 2019

| paulthomson commented<br>on 11 Nov 2019 | Collaborator | Author |  |

|-----------------------------------------|--------------|--------|--|

| Appears to be fixed!                    |              |        |  |

paulthomson closed this on 11 Nov 2019

| <> Code | lssues 30 | រឿ Pull requests 6 | Actions | III Projects 7 |  |

|---------|-----------|--------------------|---------|----------------|--|

|---------|-----------|--------------------|---------|----------------|--|

# dEQP-VK.graphicsfuzz.discard-inloop-in-function #330

Closed paulthomson opened this issue on 11 Nov 2019 · 1 comment

| 0 | paulthomson commented on 11 Nov 2019 Collaborator                                                                | Assignees                                                       |

|---|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|   | This test fails. To reproduce: amdllpc -gfxip=9.0.0 -                                                            | No one assigned                                                 |

|   | verify-ir -o temp.out *.spv<br>discard-in-loop-in-function.zip                                                   | Labels<br>None yet                                              |

|   | <ul> <li>kuhar mentioned this issue on 12 Nov 2019</li> <li>dEQP-VK.graphicsfuzz.two-nested- © Closed</li> </ul> | <b>Projects</b><br>None yet                                     |

|   | do-whiles #333                                                                                                   | <b>Milestone</b><br>No milestone                                |

|   | paulthomson commented<br>on 15 Nov 2019CollaboratorAuthor                                                        | Linked pull requests                                            |

|   | Closing as this apparently does not reproduce.                                                                   | Successfully merging a<br>pull request may close<br>this issue. |

|   | <b>paulthomson</b> closed this on 15 Nov 2019                                                                    | None yet                                                        |

|   |                                                                                                                  | 1 participant                                                   |

New issue

#### ()

# dEQP-VK.graphicsfuzz.discard-in-loop New issue #331

Closed paulthomson opened this issue on 11 Nov 2019 · 2 comments

| <> Code | () Issues 30 | រង Pull requests 6 | Actions | 🛄 Projects |

|---------|--------------|--------------------|---------|------------|

|---------|--------------|--------------------|---------|------------|

# dEQP-VK.graphicsfuzz.return-floatfrom-while-loop #332

Closed paulthomson opened this issue on 11 Nov 2019 · 11 comments

This test fails. To reproduce: amdllpc -gfxip=9.0.0 verify-ir -o temp.out \*.spv

return-float-from-while-loop.zip

nhaehnle commented on 12 Nov 2019

paulthomson commented on 11 Nov 2019

Collaborator

Collaborator

Hi Paul, aside from the fact that this is probably not a bug on the latest dev branch based on discussions on other bugs, I'd also ask you in the future to take a step back and produce higher quality bug reports.

For instance, **how** does the test fail? Does it hit an assertion or other error in the compiler? Does it generate incorrect code? Since when do these failures occur? (CTS tests are usually passing since CTS testing is performed regularly, so you should be able to find a regression point.)

Furthermore, shotgunning lots of issues like you did helps nobody. Once you've collected more information such as suggested in the previous paragraph, you will most likely find that many or even all of the issues are likely to have the same root cause (for example, they fail to compile with the same error message). It is then better to open a single issue with that error message as the title, and provide a mention of the various CTS failures that exhibit the problem in the issue body. Thank you! Assignees

No one assigned

Labels

None yet

Projects

None yet

Milestone

No milestone

#### Linked pull requests

Successfully merging a pull request may close this issue.

None yet

#### 4 participants

(!)

7

New issue

paulthomson commented on 12 Nov 2019

Collaborator Author

Apologies for the poor quality bug reports; I was indeed being slightly lazy here, as the process is not automated. Apart from not providing the log, I also forgot to add that I was using a debug build of amdIlpc when running these tests.

We are occasionally fuzzing amdllpc and creating dEQP test cases that expose the issues. The tests will always start with dEQP-VK.graphicsfuzz. But we fuzz and add tests for many tools and devices other than LLPC.

If you are indeed testing the Khronos dEQP Gerrit master branch (and perhaps pending CLs) on the debug build of the dev branch of the AMDVLK driver, then there is probably no point in me reporting these. However, I believe the debug build was possibly not being used in the past and so certain assertion failures were being missed, but perhaps this has changed.

Apologies also for creating one issue per test; other projects requested that we do this, but if you are running the tests, you will see the failures eventually anyway.

Can I ask: what is the best way to test the latest version of LLPC? Is building the dev branch of AMDVLK a fairly good approach? Is there a large delay between AMDVLK being updated to use the latest dev branch commit of LLPC? Also, feel free to let me know if assertion failures in the debug build should indeed be treated as bugs; if not, I can just use the release build.

I think bug reports in general are fine, as things do slip through cracks... for example, I believe our internal automatic testing currently doesn't have LLPC/LLVM assertions enabled (let alone runnign with anything like address sanitizer...). And thank you for the fuzzing!

Assertion failures in the compiler should absolutely be treated as bugs. Otherwise we'll just go mad over time ;)

Can I ask: what is the best way to test the latest version of LLPC? Is building the dev branch of AMDVLK a fairly good approach? Is there a large delay between AMDVLK being updated to use the latest dev branch commit of LLPC?

I'll have to punt to **@amdrexu @linqun @trenouf** on some of the details here. I suspect it's fine to use the dev branch of AMDVLK but manually track the LLPC dev branch. That really ought to work reasonably fine, and if it doesn't, we should think about how to improve the situation.

amdrexu commented on 13 Nov 2019

Collaborator

I think building latest AMDVLK dev plus latest LLPC dev is enough. LLPC has versioning mechanism. Latest LLPC can work with not-latest AMDVLK.

paulthomson commented on 15 Nov 2019

Collaborator Author

Closing as this apparently does not reproduce.

```

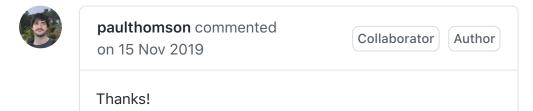

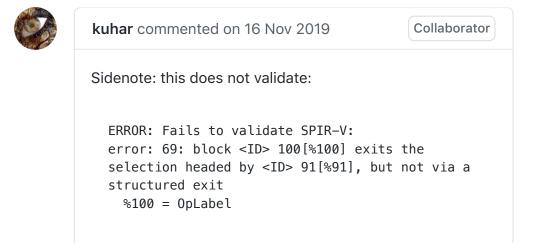

paulthomson commented on 17 Nov 2019

```

Collaborator Author

Ah this now makes sense. The failures were all validation "errors" from the old, internal version of spirv-val. The shaders validate with a newer version of spirv-val.

I could disable validation when I run amdllpc, but I chose to leave the validation on so that we would still see these "failures" and to give an incentive to update the validator version in AMDVLK. I guess the shaders won't actually be validated at run time though?

kuhar commented on 18 Nov 2019

Collaborator

I could disable validation when I run amdllpc, but I chose to leave the validation on so that we would still see these "failures" and to give an incentive to update the validator version in AMDVLK. I guess the shaders won't actually be validated at run time though?

IMO it would make sense to report inputs that pass spirvval but crash llpc with assertions/sanitizers enabled. I suppose that in real-life scenarios all shaders are known ahead of time and can be validated offline.

```

paulthomson commented

Collaborator

Author

on 18 Nov 2019

Yeah, makes sense.

E.g.

$ amdllpc discard-continue-

return.variant_fragment_shader.frag.spv

ERROR: Fails to validate SPIR-V:

error: 67: block <ID> 34[%34] exits the

selection headed by <ID> 35[%35], but not via a

structured exit

%34 = OpLabel

ERROR:

===== AMDLLPC FAILED =====

VS.

$ amdllpc -val=false discard-continue-

return.variant_fragment_shader.frag.spv

The old, buggy version of spirv-val is always run for me

unless | pass -val=false . I will add -val=false from

now on.

```

amdrexu commented on 19 Nov 2019

Collaborator

I think you can use latest codes of SPIRV-tools and build a spirv-val. Try it and if the error still exists we might report an issue ticket on SPIRV-tools repo. If the issue is gone, we will update imported SPIRV-tools source codes in spvgen.

| <> Code | (Issues 30 | រៀ Pull requests 6 | Actions | III Projects 7 | ! |

|---------|------------|--------------------|---------|----------------|---|

|         |            |                    |         |                |   |

## dEQP-VK.graphicsfuzz.two-nesteddo-whiles #333

Closed paulthomson opened this issue on 11 Nov 2019 · 5 comments

| paulthomson commented on 11 Nov 2019CollaboratorThis test fails. To reproduce: amdllpc -gfxip=9.0.0 -<br>verify-ir -o temp.out *.spvtwo-nested-do-whiles.zip | <b>Assignees</b><br>No one assigned<br><b>Labels</b><br>None yet                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| kuhar commented on 12 Nov 2019CollaboratorThis works for me on on the dev branch with assertions<br>enabled. @paulthomson                                    | Projects<br>None yet<br>Milestone<br>No milestone                                                          |

| kuhar commented on 12 Nov 2019CollaboratorAll the new issues (#330-#334) compile fine for me. Not<br>sure if the issues are still reproducible.              | <b>Linked pull requests</b><br>Successfully merging a<br>pull request may close<br>this issue.<br>None yet |

New issue

| <> Code | () Issues 30 | ל Pull requests 6 | Actions | Projects 7 | ! |

|---------|--------------|-------------------|---------|------------|---|

|---------|--------------|-------------------|---------|------------|---|

## dEQP-VK.graphicsfuzz.unreachablecontinue-statement #334

New issue

Closed paulthomson opened this issue on 11 Nov 2019 · 3 comments